Super Sylphide 進捗状況(41) -- Tiny FeatherのCPLDの中身

無人航空機(UAV)用のオートパイロットシステムSuper Sylphideの小型改良版Tiny Featherですが、処理を一手に引き受けているDSPを補助したり、機能を拡張するためにAltera MAXII CPLDを搭載しています。ようやくその中身がまともな状態になってきたので、中身を公開しようと思います。

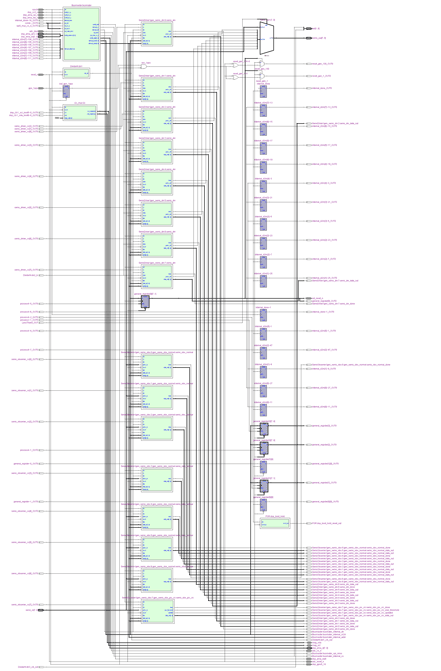

最上位階層をRTLビューワで見ると、とても綺麗です。

機能は以下に列挙するとおりです。

- 8chのラジコン受信機信号読み取り、内部レジスタに書き出し

- 8chのスピコン、サーボ用信号を内部レジスタの値に対応して生成

- ch8を使って自動および手動(受信機入力をそのままスルー出力)を切り替え

- 内部レジスタを非同期メモリとしてDSPから読み書き可能(EMIFAバス利用)

- 内部レジスタをSPIからアクセス可能

- SPIを内部レジスタ、およびFlashROM、ADCに繫ぎ変え可能(さらにUFMも)

- i2cマルチプレクス

- GPS 1ppsに同期したADCへの変換開始指令生成

- DSPを含めたシステム全体のPower on Resetを制御

- 内部の大半は俺様仕様の同期バスで接続

かなり詰め込みました。最大1270LEのうち、1016LE(80%)を使いました。また特にチューニングすることなく、fmaxは74MHzが出ており、満足しています。そのうち、個別のモジュールについても記事を書きたいと思います。

※その後、Super Sylphideに関連した成果をまとめてみました。

※※ 2011/9/30追記: 随時最新情報に更新します。現在1154LE、91%です。UFMを加えました。

コメント

コメントする

- 匿名でのコメントは受け付けておりません。

- お名前(ハンドル名可)とメールアドレスは必ず入力してください。

- メールアドレスを表示されたくないときはURLも必ず記入してください。

- コメント欄でHTMLタグは使用できません。

- コメント本文に日本語(全角文字)がある程度多く含まれている必要があります。

- コメント欄内のURLと思われる文字列は自動的にリンクに変換されます。

- 投稿ボタンを押してエラーがでなければ、投稿は成功しています。反映されるまでには少し時間がかかります。