カメラモジュール基板用のVHDL

sparkfunで売っている1.3M PixelのカメラモジュールTCM8240MDを使った基板を以前作りましたが、この度ようやくその基板に搭載されたCPLD(Max2 EPM570)用のVHDLコードがある程度動きそうな気がする(笑)ところまで完成したので、コードを公開したいと思います(アップデートした場合はこのページでお知らせします)。

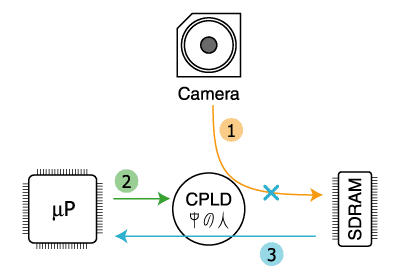

中身はこんな感じ。

別に凝ったことをしているのではなく、SDRAMをバッファとして使うためのインターフェイス回路(自動リフレッシュ制御含む)、並びにカメラ、マイコン(C8051F342)からのアクセスを切り替える機能をつけたシンプルなものです。現在システムクロックとしてマイコンが供給する48MHzを使っており、SDRAMの真価を発揮させるには至っていませんが、クロックをあげ、かつアクセスするバンクをうまく切り替えるようにすれば、カメラからの画像取り込みとマイコンへの画像吐き出しの同時処理も夢ではなさそうです。

驚いたのがMax2のLE(Logic Element)の多さです。これだけ雑多なコードでありながら、使ったLEは 214 / 570(38%) で、まだまだ入ります。CPLDではXilinxの9500シリーズ(LE144のもの)を以前使ったことがありますが、それとは比べ物にならないくらい自由度が高く、まさにFPGA感覚です。単電源で気軽に扱えるので、電子工作を趣味でやっている方にも是非お勧めしたいです。

最後にこのVHDLを書くにあたって一つはまったことをメモとして残しておきたいと思います。time型どおしの割り算はinteger型になると思っていたのですが、どうやらコンパイラの実装に依存するようです。そこである単位(例えばns)のinteger型にて表現し、シミュレーションなどでどうしてもtime型に変換したい際は、1ns * xのようにすることで解決しました。

※SDRAMコントローラにおいてPower On Reset時と自動リフレッシュ時にcsがアサートされたのを気づかないコードであったことに気づきました。2009/01/16に修正版に差し替えました。

※※SDRAMの状態遷移がかなり非効率なことに気づきました。idelをわざわざ挿入していたのをやめました。使う側についてもバーストアクセスに対応しつつあります。また各種バグがそれなりに取れたと思います。2009/01/20、さらに修正版に差し替えました。

※※※結構ヤバメのバグ取り(SDRAMのクロックのエッジが逆!!、アドレス取り込みが書き込み時のみしか取り込んでいなかった!!)、topモジュールのステートマシン化などの修正しました(2009/01/21)。シミュレータを見る限りでは、ほぼバグがとりきれたような気がしています。ついでにRev.B基板なるものを作成しました。

コメント

コメントする

- 匿名でのコメントは受け付けておりません。

- お名前(ハンドル名可)とメールアドレスは必ず入力してください。

- メールアドレスを表示されたくないときはURLも必ず記入してください。

- コメント欄でHTMLタグは使用できません。

- コメント本文に日本語(全角文字)がある程度多く含まれている必要があります。

- コメント欄内のURLと思われる文字列は自動的にリンクに変換されます。

- 投稿ボタンを押してエラーがでなければ、投稿は成功しています。反映されるまでには少し時間がかかります。