June 22, 2011

バス接続な同期応答信号をVHDLで表現

なかなか良いタイトルが思いつかなかったので苦肉の策として、とりあえずキーワードを並べてみました。何が言いたいのかもう少しまともな文章で表現すると、FPGAやCPLDの内部でさまざまなモジュールをバス接続、つまり同じ信号上に複数のモジュールをぶら下げることがあるのですが、そのモジュールからの応答をうまく受け取るにはどうしたらいいか、という話です。ごくごく当たり前のことであったのですが、ようやく考えた末に導かれた結論なので、僕自身の備忘録あらため戒めとして、記事として残しておこうと思います。

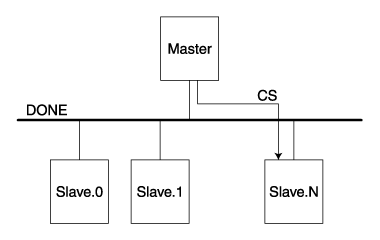

状況を図にすると、以下のような接続図になります。

CSは同時に1つの特定のモジュール(以下、スレーブNといいます)をマスタが起動要求する信号で、クロックに同期します。またDONEは全てのスレーブ(0,1,...)がバス接続されており、CSで指定されたスレーブの処理(ここではスレーブN)が終わったらLからHにクロックに同期して遷移することが望まれています。さらには、どのスレーブもCSで選択されていないときはDONEはLであることが望まれています。

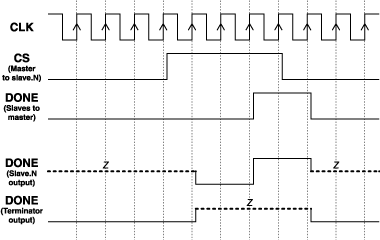

この仕様をタイミングチャートで書くと、以下のようになります。

バス接続ということでDONEは誰が責任をもって出力すればいいか、ということが重要になります。CSでスレーブNが特定されているうちは、もちろんスレーブNの責任です(タイミングチャート下から2段目)。コードで書くと以下のようになります。

ではスレーブNがない間は、誰がDONEの面倒を見てLを出力するのか、というところで悩んでしまいました。結局のところ、バスの定義があるレベルで、その機能を持てばいいと思います(タイミングチャート1番下)。コードで書くと、以下のようになります。

単純なのですが、これはバス接続の終端を行っていることに他なりません。これを忘れると、スレーブNがない場合のDONEは、合成ツールが勝手に決めてしまうので気持ちが悪い、という事態が発生します。終端を忘れないように記録に残しておくことにしました。

コメント

コメントする

スポンサード リンク