September 23, 2011

Super Sylphide 進捗状況(45) -- CPLD で SPI MUX

無人航空機(UAV)用の次期オートパイロット装置Tiny Featherを開発中です。前回は搭載されたCPLDの中身についてi2cに関する記事でしたが、今回はその続きでSPIについて紹介します。題してSPI MUX(マルチプレクサ)。

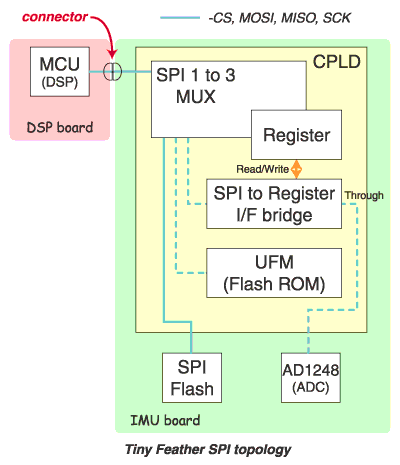

中身の模式図をいきなり出してしまうことにします。

図のように、マスタのDSPから生えている1つのSPIバスを、CPLDを介して4つのスレーブデバイスで共有しています。順に紹介すると、Flash ROM、ADS1248(24 bit AD変換機)、MAXII User Flash Memory(UFM)、バスブリッジ(SPI、およびCPLD内のレジスタインターフェイスを中継しています)です。前2者は独立したデバイスなのに対して、後2者はCPLD内に実装されています。

スレーブデバイスの切り替えはCPLD内のレジスタを介して行われます。切り替えはFlash ROM、MAXII UFM、バスブリッジの3者間で行われますが、前2者はブート時のみしかアクセスしないのに対して、バスブリッジ、およびそこから生えているADS1248はブート以降に使うことを考慮しての設計になっています。なお、切り替えに使うレジスタは別経路(Asynchronous Memory I/F)でもアクセスが可能です。また、バスブリッジの中身については別の記事でそのうち紹介したいと思います。

SPIはi2cに比べるとはるかに単純で、入力と出力に使う配線が物理的に切り分けられているため、とても使いやすいです。しかしながらデバイスが増えると配線が増えてしまうのが困りものです。そこで今回紹介したように、一回CPLDで受けることで、配線の自由度を増すとともに配線数を極小化できました。

例によってコードを置いておきます。CPLDの中身の全コードはこのあたりにあるのですが、今回の部分は最上位であるtop.vhdに主に書かれています。

※続いて、Tiny Featherの誘導制御の骨組みを公開しました。

※※ADSが外部機器としてつながるようになったため、現在SPI MUXはさらに複雑になっています。図でいうと、ADCと並列にADSがアドレスによって洗濯できるようになりました。